KLA Investor Conference Presentation Deck

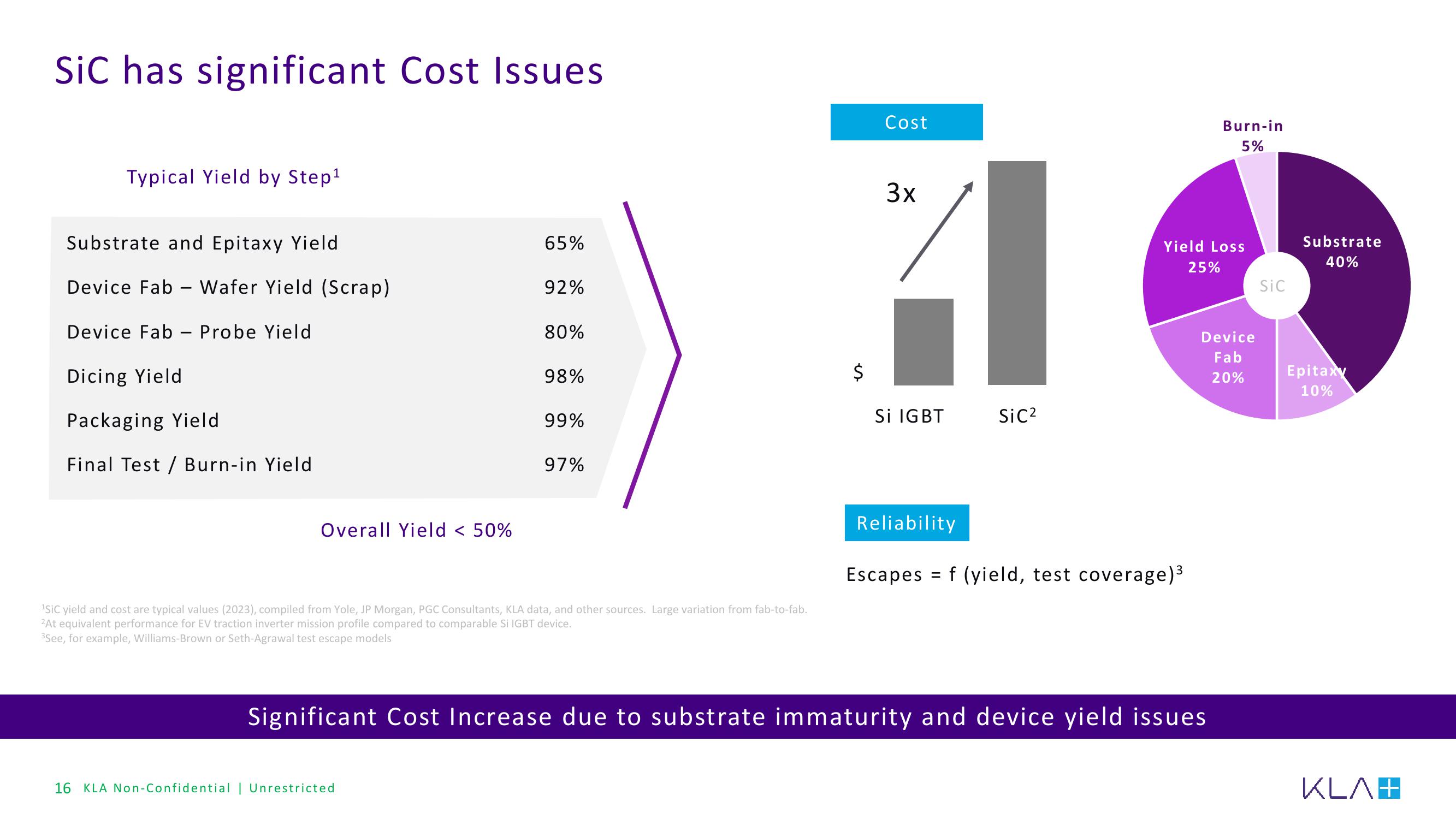

SiC has significant Cost Issues

Typical Yield by Step¹

Substrate and Epitaxy Yield

Device Fab Wafer Yield (Scrap)

Device Fab - Probe Yield

Dicing Yield

Packaging Yield

Final Test / Burn-in Yield

-

Overall Yield < 50%

65%

92%

16 KLA Non-Confidential | Unrestricted

80%

98%

99%

97%

¹SiC yield and cost are typical values (2023), compiled from Yole, JP Morgan, PGC Consultants, KLA data, and other sources. Large variation from fab-to-fab.

2At equivalent performance for EV traction inverter mission profile compared to comparable Si IGBT device.

³See, for example, Williams-Brown or Seth-Agrawal test escape models

Cost

3x

1

$

Si IGBT

Reliability

SIC²

Yield Loss

25%

Escapes = f (yield, test coverage)³

Burn-in

5%

Significant Cost Increase due to substrate immaturity and device yield issues

Device

Fab

20%

Sic

Substrate

40%

Epitaxy

10%

KLA+View entire presentation